Hdl系列 半加器 全加器和行波进位加法器原理与设计 知乎

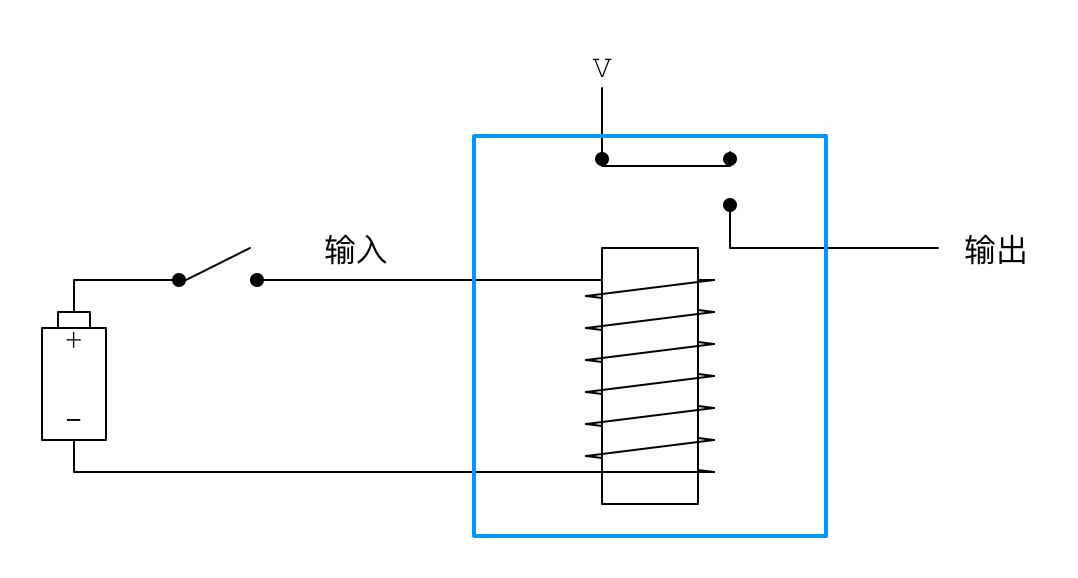

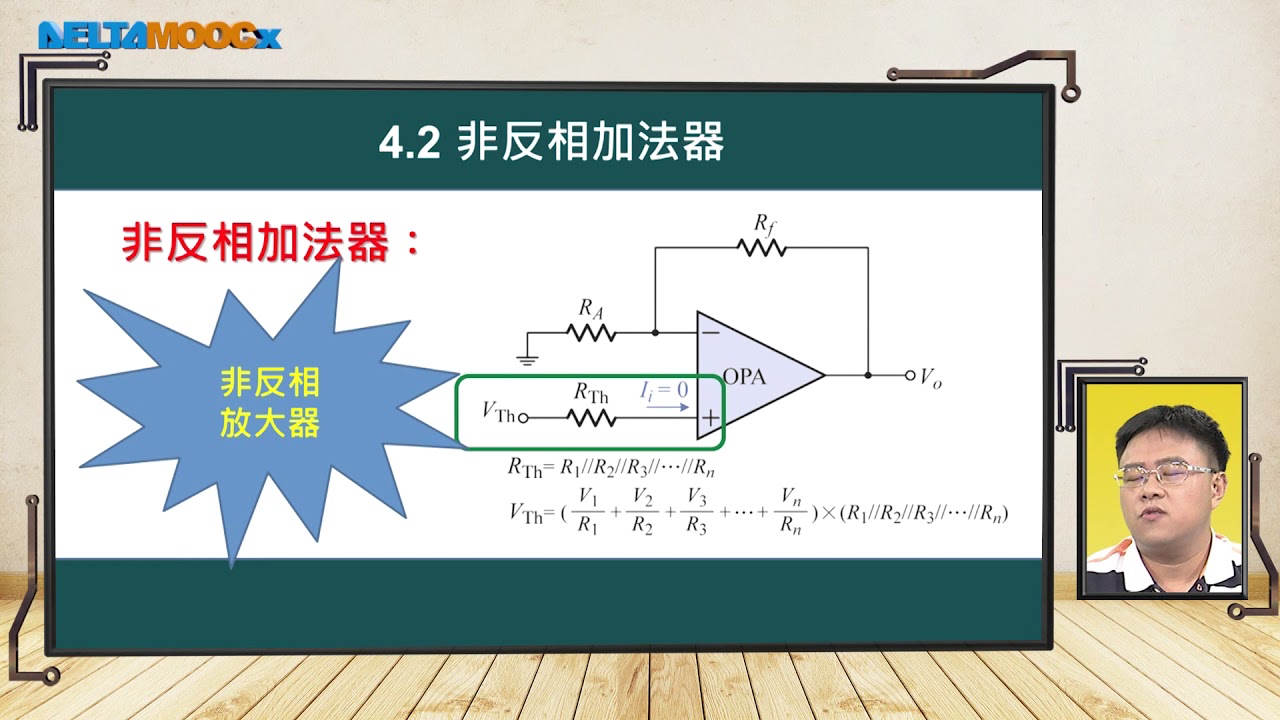

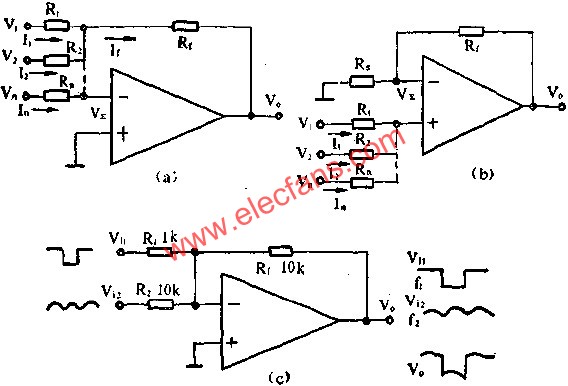

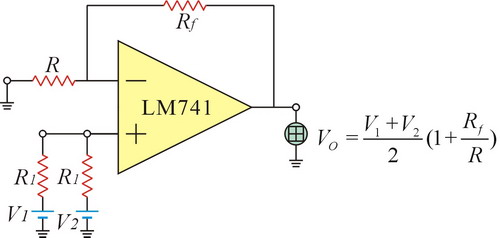

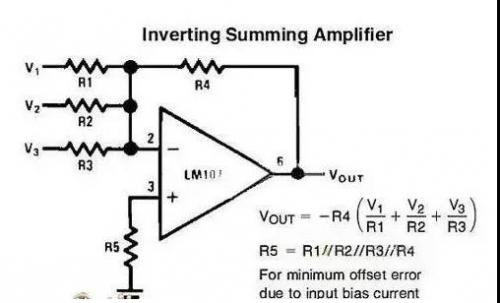

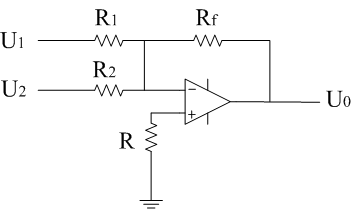

第10章 運算放大器 101 運算放大器的簡介 102 反相與非反相放大器 103 加法器與減法器 104 微分器與積分器 105 比較器 接在麵包板上老師說不能跨線 但是那麼亂要怎麼不跨阿 還只能用六個ic 我陷入了疑惑。。。 我上網搜尋加法器大多跨的亂七八糟的 我滿頭問號 怎麼想都會撞在一起 如果不用考慮跨線 就默默的接上去 一個小時可以完成 但是考慮跨線 我陷入了流裡

加法器电路图

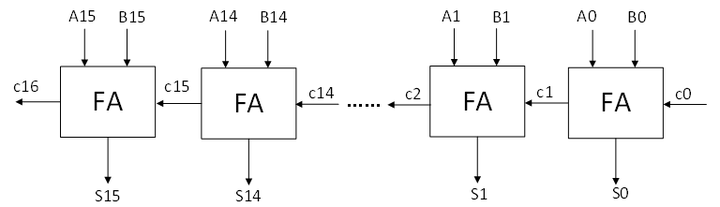

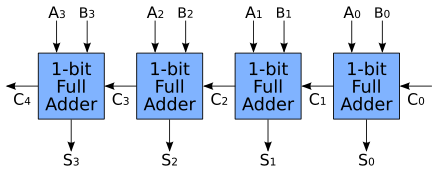

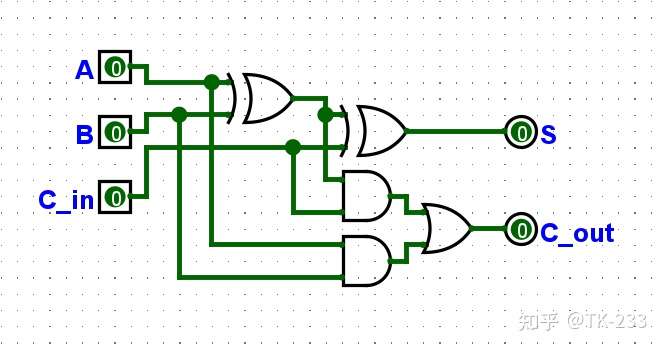

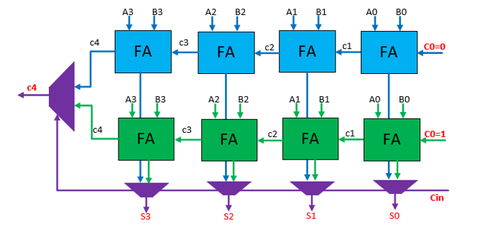

加法器电路图-利用4bit加法器組合出8bit ripplecarry adder加法器 請同學先鍵入下列程式碼,並且將空白處填完後,再按一次存檔 Computer ArchitectureVerilog HDL(简称 Verilog )是一种硬件描述语言,用于数字电路的系统设计。可对算法级、门级、开关级等多种抽象设计层次进行建模。 Verilog 继承了 C 语言的多种操作符和结构,与另一种硬件描述语言 VHDL 相比,语法不是很严格,代码更加简洁,更容易上手。

加法器 搜狗百科

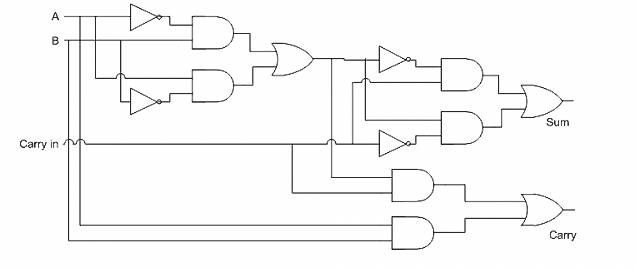

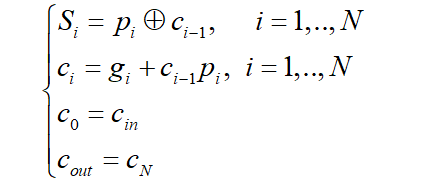

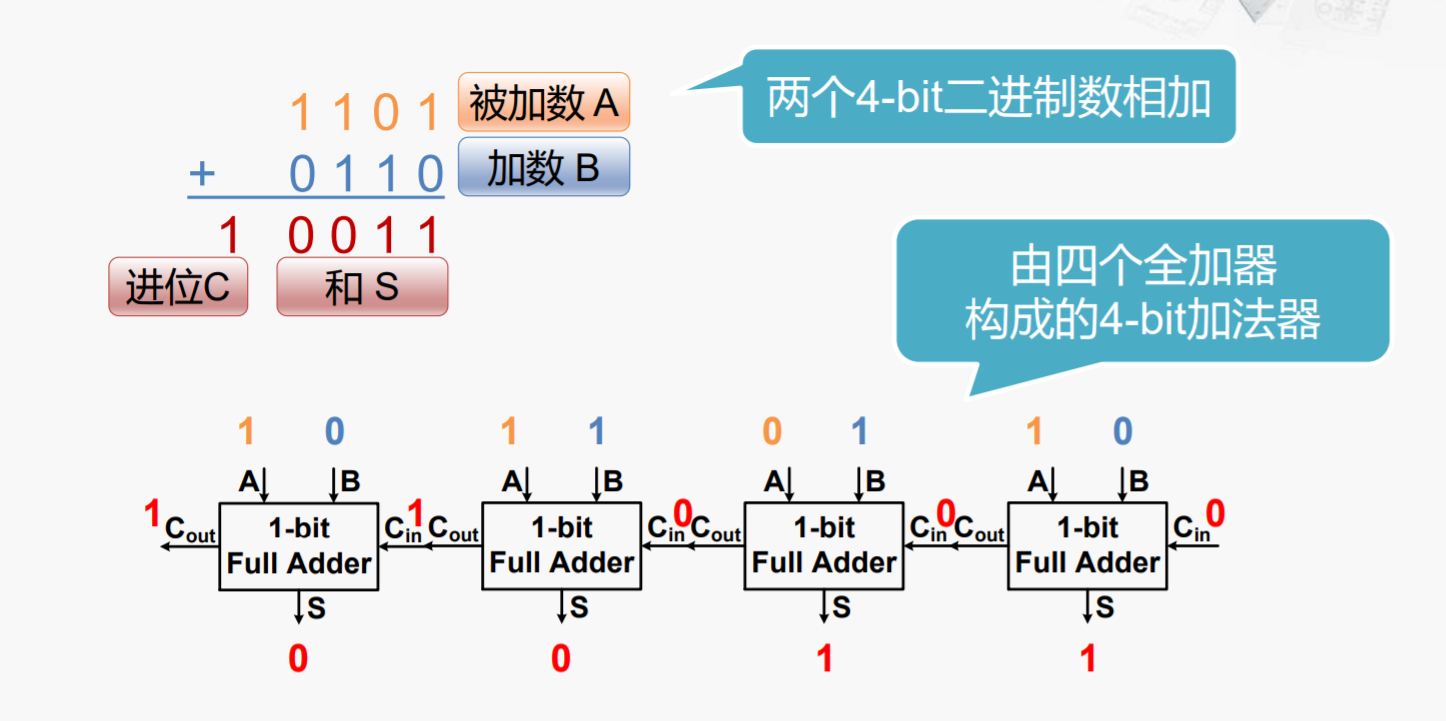

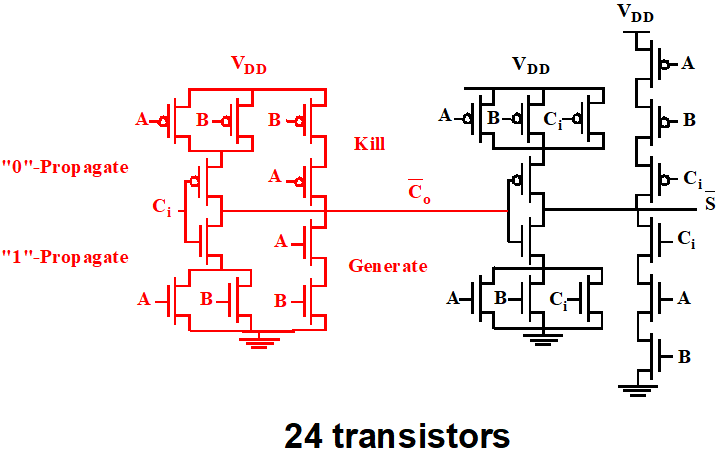

底下還是加法器 而上面我們有4個4bit的carry look ahead unit 它們會做的事情就是去計算carry 注意 它們一次只能算出4個bit的carry 所以假設一開始我們給定了propargate以及generate還有Cin 當我們給定了這些值之後 最底下的 也就是最後一個4bit的carry look ahead unit 它的值都本系列文章将向大家推荐一个学习 Verilog 的好去处:HDLBits HDLBits 在提供 Verilog 基础语法教程的同时,还能够在线仿真你的 Verilog 模块,将你的输出与正确的时序比较,可以说真的是很棒了。Wire加法器/減法器 1 圖4 是2 的補數加法/減法器,c 0 = 0 則為一加法器,c 0 = 1 則為一減法器,最高次位 (msb) 為符號元,0 表正數,1 為負數。 2 按圖4 插妥電路,置sw 1 ~sw 8 如表9 所示,並記錄對應的l 1 ~l 4 輸出於表中。 3

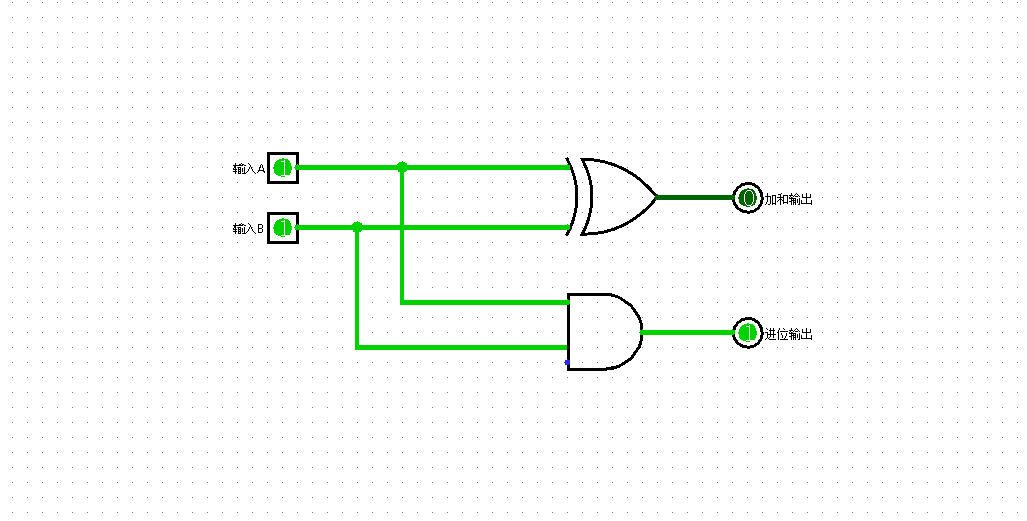

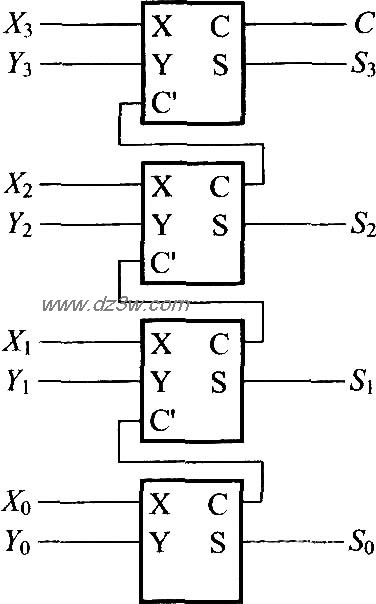

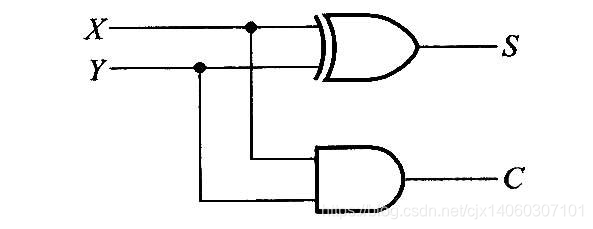

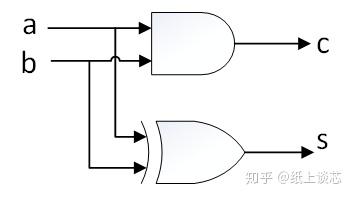

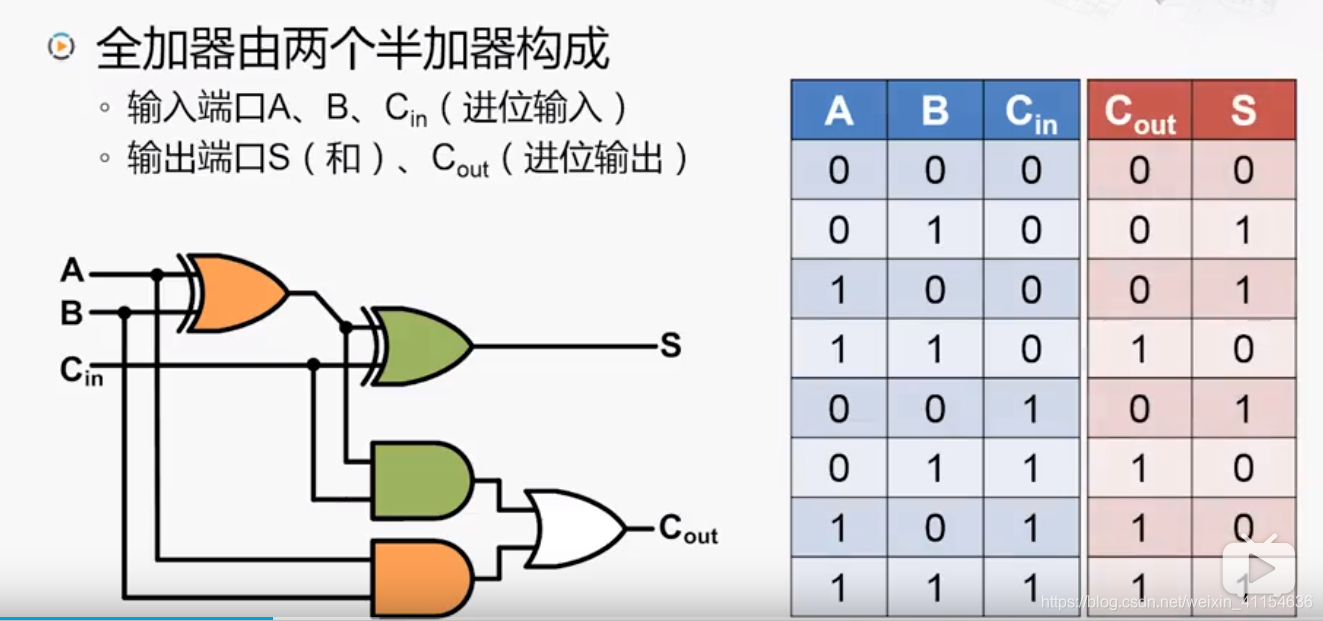

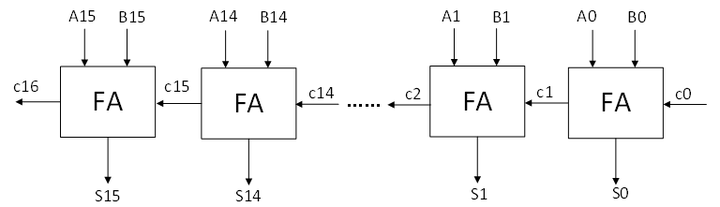

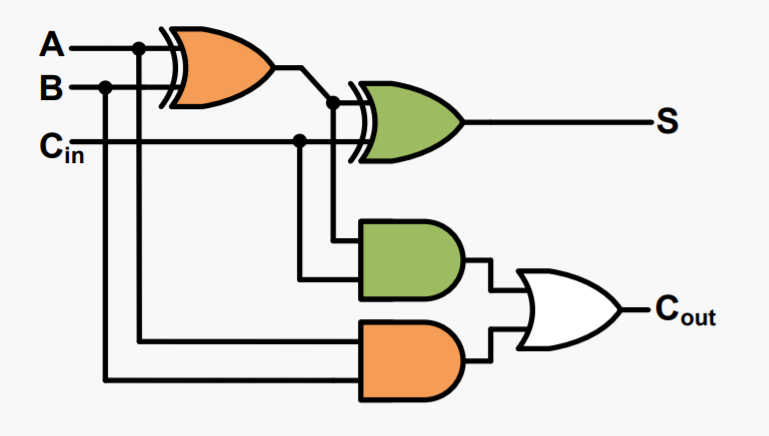

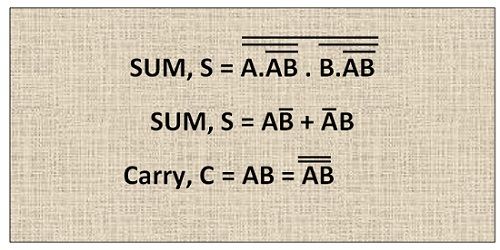

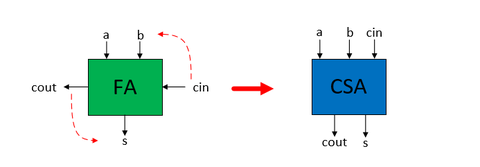

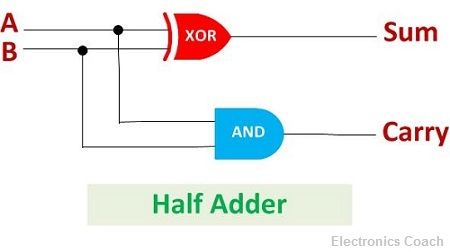

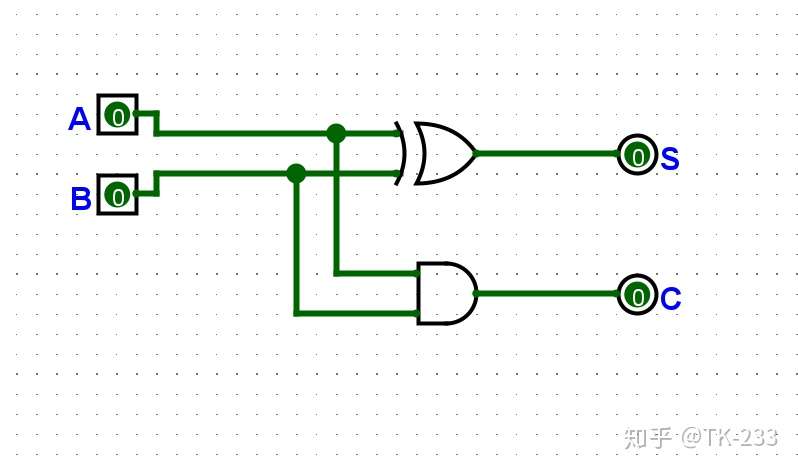

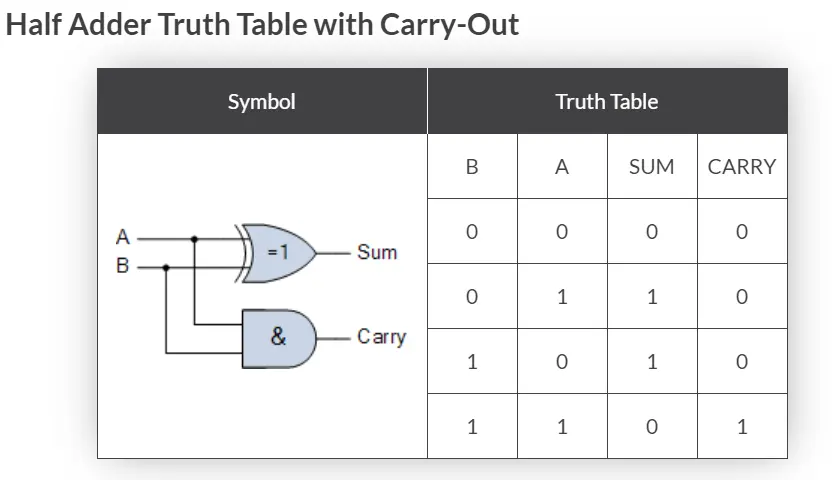

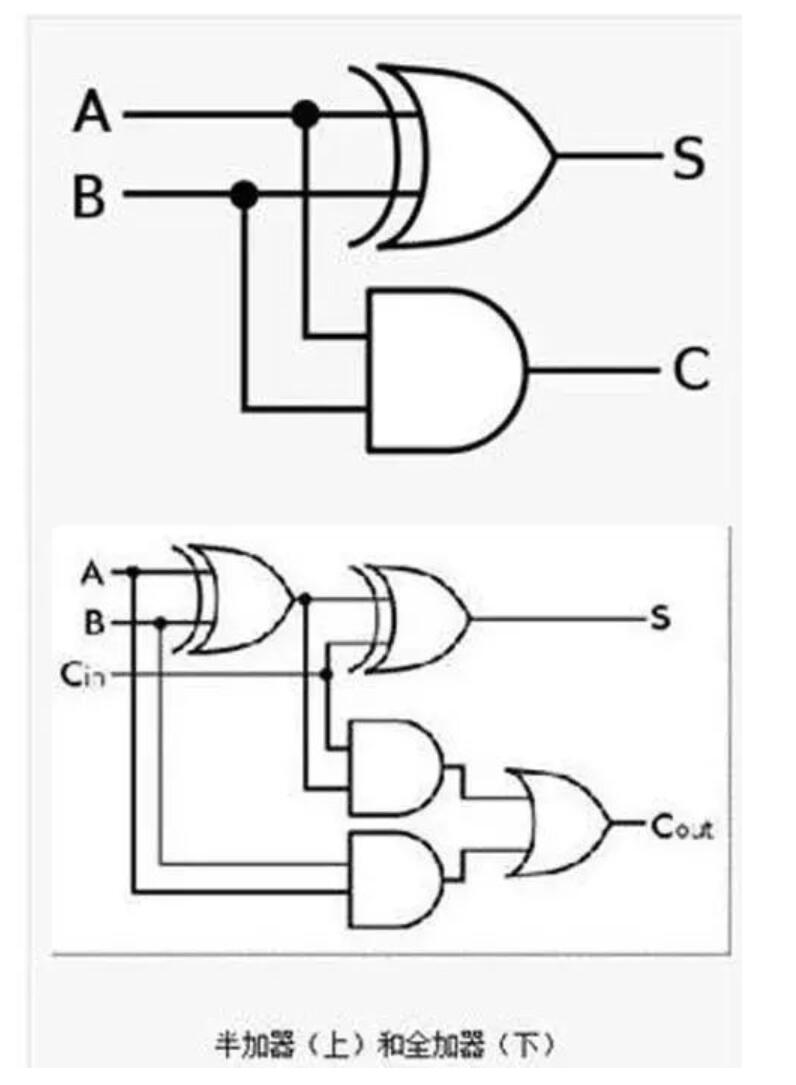

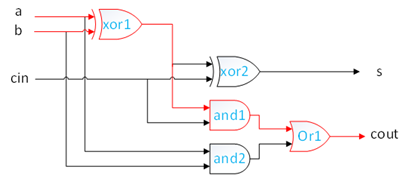

关键词:while, for, repeat, forever Verilog 循环语句有 4 种类型,分别是 while,for,repeat,和 forever 循环。循环语句只能在 always 或 initial 块中使用,但可以包含延迟表达式。 while 循环 while 循环语法格式如下: while (condition) begin end while 循环中止条件为 condition 为假。當我們在設計加法器電路時,如果每一位運算都必須等待前一位數是否進位將造成速度的降低,於是我們需要設計邏輯電路來快速產生是否進位的訊息。 給定一正整數 ,傳回第 位進位的布林函數。 但是因為每個 bit 在計算時必須等待前一個 bit 計算得到的 carry532 全加法器 前一小節介紹的一位元加法器(半加法器),其輸入的加數與被加數都是一位元。 但是當輸入的加數與被加數是一個位元以上時,會需要一個多位元的加法器。最 常見的多位元加法器有兩種:漣波進位加法器(ripple carry adder) 和進位前看加

加法器电路图のギャラリー

各画像をクリックすると、ダウンロードまたは拡大表示できます

| ||

|  | |

|  | |

「加法器电路图」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

|  |  |

|  |  |

「加法器电路图」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  | |

| ||

「加法器电路图」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  | |

|  |  |

「加法器电路图」の画像ギャラリー、詳細は各画像をクリックしてください。

| ||

|  |  |

|  |  |

「加法器电路图」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  |  |

|  |  |

「加法器电路图」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  |  |

|  |  |

「加法器电路图」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  | |

| ||

「加法器电路图」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

|  |  |

|  | |

「加法器电路图」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |  |

|  | |

|  | |

「加法器电路图」の画像ギャラリー、詳細は各画像をクリックしてください。

|  | |

|  | |

|  |  |

「加法器电路图」の画像ギャラリー、詳細は各画像をクリックしてください。

|  |

問題研討 試比較漣波進位加法器與前視進位加法器的 優缺點 試設計一個能完成兩個千位數相加之十進制 加法器加法器進行模擬比較,並對利用前瞻加法器所設計之4 4 乘法器進行模擬,模擬 結果如下,其中所使用的供應電壓為33 伏特。 圖十一4bit 前瞻加法器模擬結果 圖十一為4bit 前瞻加法器模擬結果,波形由上而下分別是圖八中之b0 s s1 s2 s3 其中輸入訊號頻率為100MHz。

Incoming Term: 加法器, 加法器电路, 加法器原理, 加法器电路图, 加法器采用先行进位的目的是, 加法器真值表, 加法器实验报告, 加法器设计, 加法器 减法器, 加法器 运放, 加法器电路设计,

0 件のコメント:

コメントを投稿